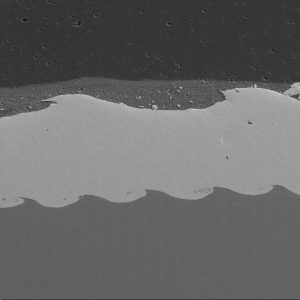

This is a BSE SEM image of a glass rectifier diode that was chemically decapsulated to remove the glass case.

This is the diode die, which showed two separate breakdown sites that likely occurred simultaneously.

The die fractures are due to thermal shock due to the thermal effect rapid quenching by the surrounding die material immediately after the event.

This type of breakdown is likely due to a fast voltage transient.